Сумматор (электроника) - Adder (electronics)

| Часть серии по | |||||||

| арифметико-логические схемы | |||||||

|---|---|---|---|---|---|---|---|

| Быстрая навигация | |||||||

Составные части

| |||||||

Категории

| |||||||

Смотрите также | |||||||

An сумматор это цифровая схема который выполняет добавление чисел. во многих компьютеры и другие виды процессоры сумматоры используются в арифметико-логические устройства или же ALU. Они также используются в других частях процессора, где используются для расчета адреса, индексы таблицы, операторы увеличения и уменьшения и аналогичные операции.

Хотя сумматоры можно построить для многих числовые представления, Такие как двоично-десятичный или же превышение-3, самые распространенные сумматоры работают на двоичные числа.В случаях, когда два дополнения или же дополнение используется для представления отрицательные числа, легко превратить сумматор в сумматор – вычитатель.Другой представление числа со знаком требуется больше логики в отношении базового сумматора.

Двоичные сумматоры

Полусумматор

В полусумматор добавляет две одиночные двоичные цифры А и B. Имеет два выхода, сумма (S) и нести (C). Сигнал переноса представляет собой переполнение в следующую цифру многозначного сложения. Стоимость суммы составляет 2C + S. Самая простая конструкция полусумматора, изображенная справа, включает в себя Ворота XOR за S и И ворота за C. Логическая логика для суммы (в данном случае S) будет A'B + AB ′ тогда как для переноски (C) будет AB. С добавлением ИЛИ ворота для объединения их выходов переноса два полусумматора могут быть объединены в полный сумматор.[1] Полусумматор складывает два входных бита и генерирует перенос и сумму, которые являются двумя выходами полусумматора. Вход переменные полусумматора называются дополнительным и дополнительным битами. Выходные переменные - это сумма и перенос. В таблица истинности для полусумматора:

Входы Выходы А B C S 0 0 0 0 1 0 0 1 0 1 0 1 1 1 1 0

Полный сумматор

А полный сумматор складывает двоичные числа и учитывает как входящие, так и исходящие значения. Однобитовый полный сумматор складывает три однобитовых числа, часто записываемых как А, B, и Cв; А и B операнды, и Cв немного перенесен из предыдущего менее значимого этапа.[2] Полный сумматор обычно является компонентом каскада сумматоров, которые складывают 8, 16, 32 и т. Д. Двоичные числа. Схема выдает двухбитный выходной сигнал. Выходной перенос и сумма обычно представлены сигналами Cиз и S, где сумма равна 2Cиз + S.

Полный сумматор может быть реализован разными способами, например, с помощью специального транзистор -уровневый контур или состоящий из других ворот. Один пример реализации с S = А ⊕ B ⊕ Cв и Cиз = (А ⋅ B) + (Cв ⋅ (А ⊕ B)).

В этой реализации последний ИЛИ ворота до того, как выносной вывод может быть заменен Ворота XOR без изменения итоговой логики. Использование только двух типов вентилей удобно, если схема реализуется с использованием простых Интегральная схема чипы, которые содержат только один тип ворот на чип.

Полный сумматор можно также построить из двух полусумматоров, подключив А и B на вход одного полусумматора, затем взяв его сумму-выход S как один из входов второго полусумматора и Cв в качестве другого входа, и, наконец, выходы переноса от двух полусумматоров подключаются к логическому элементу ИЛИ. Выходная сумма второй полусумматора является окончательным выходом суммы (S) полного сумматора, а выход логического элемента ИЛИ является окончательным выходом переноса (Cиз). Критический путь полного сумматора проходит через оба логических элемента XOR и заканчивается на суммирующем бите. s. Предполагая, что вентиль XOR требует 1 задержки для завершения, задержка, вызванная критическим путем полного сумматора, равна

Критический путь переноса проходит через один вентиль XOR в сумматоре и через 2 логических элемента (AND и OR) в блоке переноса, и поэтому, если логическим элементам AND или OR требуется 1 задержка для завершения, задержка составляет

В таблица истинности для полного сумматора:

Входы Выходы А B Cв Cиз S 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1

Сумматоры, поддерживающие несколько битов

Сумматор с пульсацией

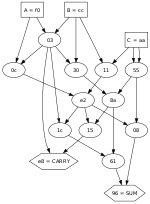

Можно создать логическую схему, используя несколько полных сумматоров для добавления N-битовые числа. Каждый полный сумматор вводит Cв, какой Cиз предыдущего сумматора. Такой сумматор называется сумматор с волновым переносом (RCA), поскольку каждый бит переноса "перетекает" на следующий полный сумматор. Обратите внимание, что первый (и только первый) полный сумматор можно заменить полусумматором (при условии, что Cв = 0).

Компоновка сумматора с волновым переносом проста, что позволяет сократить время разработки; однако сумматор с переносом пульсаций работает относительно медленно, поскольку каждый полный сумматор должен ждать, пока бит переноса будет вычислен из предыдущего полного сумматора. В задержка ворот можно легко вычислить, проверив полную схему сумматора. Каждый полный сумматор требует трех уровней логики. В 32-битном сумматоре с переносом пульсации имеется 32 полных сумматора, поэтому задержка критического пути (наихудший случай) равна 3 (от входа до переноса в первом сумматоре) + 31 × 2 (для распространения переноса в последних сумматорах) = 65 задержки выхода на посадку.[3]Общее уравнение для задержки наихудшего случая для п-битовый сумматор пульсации переноса, учитывающий как сумму, так и биты переноса,

Конструкция с чередующимися полярностями переноса и оптимизированная И-ИЛИ-Инвертировать ворота могут быть примерно в два раза быстрее.[4]

Сумматор с упреждением

Чтобы сократить время вычислений, инженеры разработали более быстрые способы сложения двух двоичных чисел с помощью сумматоры с упреждением (CLA). Они работают, создавая два сигнала (п и грамм) для каждой битовой позиции, в зависимости от того, распространяется ли перенос из менее значимой битовой позиции (по крайней мере, один вход равен 1), генерируется в этой битовой позиции (оба входа равны 1) или уничтожается в этой битовой позиции (оба входы равны 0). В большинстве случаев, п это просто сумма вывода полусумматора и грамм - выход переноса того же сумматора. После п и грамм генерируются, создаются переносы для каждой битовой позиции. Некоторые передовые архитектуры с упреждающим просмотром - это Манчестерская цепочка для переноски, Гадюка Брента-Кунга (BKA),[5] и Когге – Стоун гадюка (KSA).[6][7]

Некоторые другие архитектуры многобитового сумматора разбивают сумматор на блоки. Можно изменять длину этих блоков в зависимости от Задержка распространения схем для оптимизации времени вычислений. Эти блочные сумматоры включают сумматор с пропуском переноса (или обходом переноса) что определит п и грамм значения для каждого блока, а не для каждого бита, и переносной сумматор который предварительно генерирует сумму и значения переноса для любого возможного ввода переноса (0 или 1) в блок, используя мультиплексоры для выбора соответствующего результата когда бит переноса известен.

Комбинируя несколько сумматоров с опережающим переносом, можно создавать сумматоры еще большего размера. Это можно использовать на нескольких уровнях для создания еще более крупных сумматоров. Например, следующий сумматор представляет собой 64-битный сумматор, который использует четыре 16-битных CLA с двумя уровнями опережающие транспортные единицы.

Другие конструкции сумматора включают переносной сумматор, сумматор условной суммы, сумматор, и полный сумматор.

Сумматоры Carry-save

Если схема сложения должна вычислять сумму трех или более чисел, может быть полезно не распространять результат переноса. Вместо этого используются трехвходовые сумматоры, дающие два результата: сумму и перенос. Сумма и перенос могут подаваться на два входа последующего сумматора с 3 числами, не дожидаясь распространения сигнала переноса. Однако после всех этапов сложения для объединения итоговой суммы и результатов переноса необходимо использовать обычный сумматор (например, волновой перенос или опережающий просмотр).

3: 2 компрессора

Полный сумматор можно рассматривать как 3: 2 компрессор с потерями: он суммирует три однобитовых ввода и возвращает результат как одно двухбитное число; то есть он отображает 8 входных значений на 4 выходных значения. Таким образом, например, двоичный вход 101 приводит к выходу 1 + 0 + 1 = 10 (десятичное число 2). Выполнение представляет собой один бит результата, а сумма представляет собой нулевой бит. Точно так же полусумматор можно использовать как 2: 2 компрессор с потерями, сжимая четыре возможных входа в три возможных выхода.

Такие компрессоры можно использовать для ускорения суммирования трех или более слагаемых. Если слагаемых ровно три, макет известен как переносной сумматор. Если слагаемых четыре или более, необходимо более одного уровня компрессоров, и существуют различные возможные конструкции для контура: наиболее распространенными являются Дадда и Деревья Уоллеса. Этот вид схемы чаще всего используется в множители, поэтому эти схемы также известны как множители Дадды и Уоллеса.

Смотрите также

- Вычитатель

- Электронный микшер - для добавления аналоговых сигналов

Рекомендации

- ^ Ланкастер, Джеффри А. (2004). Дизайн и разработка программного обеспечения Excel HSC. Паскаль Пресс. п. 180. ISBN 978-1-74125175-3.

- ^ Мано, М. Моррис (1979). Цифровая логика и компьютерный дизайн. Prentice-Hall. стр.119–123. ISBN 978-0-13-214510-7.

- ^ Сатпатия, Пинаки (2016). Разработка и реализация сумматора Carry Select с использованием T-Spice. Якорное академическое издательство. п. 22. ISBN 978-3-96067058-2.

- ^ Берджесс, Нил (2011). Сумматоры с быстрым переносом пульсаций в КМОП СБИС со стандартной ячейкой. 20-й симпозиум IEEE по компьютерной арифметике. С. 103–111.

- ^ Брент, Ричард Пирс; Кунг, Сян Дэ (март 1982). «Обычный макет для параллельных сумматоров». Транзакции IEEE на компьютерах. С-31 (3): 260–264. Дои:10.1109 / TC.1982.1675982. ISSN 0018-9340. S2CID 17348212.

- ^ Когге, Питер Майкл; Стоун, Гарольд С. (август 1973 г.). «Параллельный алгоритм эффективного решения общего класса рекуррентных уравнений». Транзакции IEEE на компьютерах. С-22 (8): 786–793. Дои:10.1109 / TC.1973.5009159. S2CID 206619926.

- ^ Рейндерс, Неле; Дехайн, Вим (2015). Сверхнизковольтная конструкция энергоэффективных цифровых схем. Аналоговые схемы и серия обработки сигналов. Аналоговые схемы и обработка сигналов (ACSP) (1-е изд.). Чам, Швейцария: Springer International Publishing AG, Швейцария. Дои:10.1007/978-3-319-16136-5. ISBN 978-3-319-16135-8. ISSN 1872-082X. LCCN 2015935431.

дальнейшее чтение

- Лю, Цо-Кай; Хохулин, Кейт Р .; Шиау, Лих-Эр; Мурога, Сабуро (январь 1974 г.). «Оптимальные однобитовые полные сумматоры с разными типами вентилей». Транзакции IEEE на компьютерах. Bell Laboratories: IEEE. С-23 (1): 63–70. Дои:10.1109 / T-C.1974.223778. ISSN 0018-9340. S2CID 7746693.

- Лай, Хунг Чи; Мурога, Сабуро (сентябрь 1979 г.). «Минимальные двоичные параллельные сумматоры с вентилями NOR (NAND)». Транзакции IEEE на компьютерах. IEEE. С-28 (9): 648–659. Дои:10.1109 / TC.1979.1675433. S2CID 23026844.

- Мид, Карвер; Конвей, Линн (1980) [декабрь 1979]. Введение в системы СБИС (1-е изд.). Ридинг, Массачусетс, США: Эддисон-Уэсли. Bibcode:1980aw ... книга ..... M. ISBN 978-0-20104358-7. Получено 2018-05-12.

- Давио, Марк; Дешам, Жан-Пьер; Тэйз, Андре (1983). Цифровые системы с реализацией алгоритма (1-е изд.). Исследовательская лаборатория Philips, Брюссель, Бельгия: Джон Уайли и сыновья, публикация Wiley-Interscience. ISBN 978-0-471-10413-1. LCCN 82-2710.

внешняя ссылка

- Аппаратные алгоритмы для арифметических модулей, включает описание нескольких схем сумматора с фигурами.

- 8-битный полный сумматор и вычитатель, демонстрация интерактивного полного сумматора, встроенного в JavaScript, исключительно в учебных целях.

- Интерактивное моделирование полного сумматора (требуется Java), Интерактивная схема полного сумматора, созданная с помощью онлайн-симулятора схем Teahlab.

- Интерактивное моделирование полусумматора (требуется Java), схема Half Adder, созданная с помощью симулятора схем Teahlab.

- 4-битное моделирование полного сумматора построен в Verilog, и сопутствующие Видеоурок по Ripple Carry Full Adder

- Ширрифф, Кен (ноябрь 2020 г.). «Обратный инжиниринг схемы переноса вперед в процессоре Intel 8008».