Программируемая логическая матрица - Programmable logic array - Wikipedia

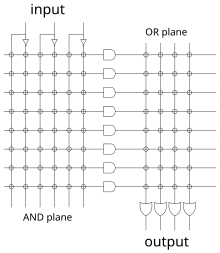

А программируемая логическая матрица (PLA) является своего рода программируемое логическое устройство используется для реализации комбинационная логика схемы. PLA имеет набор программируемых И ворота самолеты, которые связаны с набором программируемых ИЛИ ворота плоскости, которые затем можно условно дополнить для получения результата. Имеет 2N Логические элементы И для N входных переменных и для M выходов из PLA должны быть M вентилей ИЛИ, каждый с программируемыми входами от всех вентилей И. Этот макет позволяет синтезировать множество логических функций в сумме продуктов. канонические формы.

PLA отличаются от Программируемая логика массива устройства (PAL и GAL ) в том, что обе плоскости логического элемента И и ИЛИ являются программируемыми.

История

В 1970 г. Инструменты Техаса разработал маска -программируемая ИС на основе IBM ассоциативная память только для чтения или ROAM. Это устройство, TMS2000, было запрограммировано путем изменения металлического слоя во время изготовления ИС. TMS2000 имел до 17 входов и 18 выходов с 8 триггерами JK для памяти. TI ввел термин Программируемый логический массив для этого устройства.[1]

Порядок реализации

- Подготовка в СОП (сумма продуктов ) форма.

- Получите минимальную форму СОП, чтобы свести количество терминов к продукту до минимума.

- Определите входное соединение матрицы И для генерации требуемого члена продукта.

- Затем определите входные соединения матрицы ИЛИ для генерации сумм.

- Определите соединения инвертированной матрицы.

- Запрограммируйте PLA.

Блок-схема PLA:

| 1-Й БЛОК | 2-Й БЛОК | 3-Й БЛОК | 4-Й БЛОК | 5 БЛОК |

|---|---|---|---|---|

| ВХОДНОЙ БУФЕР | И МАТРИЦА | ИЛИ МАТРИЦА | ИНВЕРТИРОВАТЬ / НЕ ИНВЕРТИРОВАТЬ МАТРИЦУ | ВЫХОДНОЙ БУФЕР FLIP FLOP |

Преимущества перед постоянной памятью

Желаемые выходы для каждой комбинации входов мог быть запрограммированным в только для чтения памяти, причем входы управляются адресной шиной, а выходы считываются как данные. Однако для этого потребуется отдельная ячейка памяти для каждый возможная комбинация входных данных, включая комбинации, которые никогда не должны возникать, а также дублирование данных для условий "безразлично" (например, логика типа "если вход A равен 1, то, что касается выхода X, мы неважно, что это за вход B »: в ПЗУ это должно быть записано дважды, по одному разу для каждого возможного значения B, и по мере добавления дополнительных входов« безразлично »дублирование растет экспоненциально); следовательно, массив программируемой логики часто может реализовать часть логики с использованием меньшего количества транзисторов, чем эквивалент в постоянной памяти. Это особенно ценно, когда он является частью микросхемы обработки, где мало транзисторов (например, исходный 6502 Чип содержал PLA для управления различными операциями процессора[2]).

Приложения

Одно из применений PLA - реализовать контроль над путь к данным. Он определяет различные состояния в наборе команд и создает следующее состояние (условным ветвлением). [например. если машина находится в состоянии 2, и перейдет в состояние 4, если инструкция содержит немедленное поле; тогда PLA должен определить действия элемента управления в состоянии 2, установит следующее состояние равным 4, если инструкция содержит немедленное поле, и определит действия элемента управления в состоянии 4]. Программируемые логические массивы должны соответствовать диаграмма состояний для системы.

В Коммодор 64 В домашнем компьютере, выпущенном в 1982 году, для обработки системных сигналов использовалась «906114-01 PLA».[3]

Смотрите также

Рекомендации

- ^ Андрес, Кент (октябрь 1970 г.). Отчет по применению Texas Instruments: массивы программируемой логики MOS. Инструменты Техаса. Бюллетень СА-158.

- ^ Как на самом деле работают нелегальные коды операций MOS 6502

- ^ arcadecomponents.com - Commodore 906114-01 64 PLA IC

внешняя ссылка

- «Программируемый логический массив (PLA)». cmsc311. Университет Мэриленда. 2003. Архивировано с оригинал на 2017-12-14.

- «PLA (программируемая логическая матрица)». Java-апплет. Гамбургский университет. Архивировано из оригинал на 2013-01-15. Получено 2010-04-07.