Логика NAND - NAND logic

В Булева функция NAND имеет свойство функциональная полнота. Это означает, что любое логическое выражение может быть повторно выражено с помощью эквивалент выражение с использованием Только NAND операции. Например, функция НЕ (x) может быть эквивалентно выражена как И-НЕ (x, x). В области цифровые электронные схемы, это означает, что мы можем реализовать любой Логическая функция используя только Ворота NAND.

Математическое доказательство этого было опубликовано Генри М. Шеффер в 1913 г. в Труды Американского математического общества (Шеффер 1913). Аналогичный случай применим к Функция ИЛИ, и это называется НИ логика.

NAND

Ворота NAND - это перевернутый И ворота. Он имеет следующую таблицу истинности:

| ||||||||||||||||

Q = А NAND B

| ||||||||||||||||

Создание других вентилей с использованием вентилей NAND

Шлюз NAND - это универсальный шлюз, что означает, что любой другой вентиль может быть представлен как комбинация вентилей NAND.

НЕТ

Логический элемент НЕ создается путем соединения входов логического элемента И-НЕ вместе. Поскольку вентиль И-НЕ эквивалентен вентилю И, за которым следует вентиль НЕ, при объединении входов логического элемента И-НЕ остается только вентиль НЕ.

| Желаемый НЕ Ворота | Строительство NAND | ||||||

|---|---|---|---|---|---|---|---|

|  | ||||||

| Q = НЕ ( А ) | = А NAND А | ||||||

| |||||||

И

Логический элемент И создается путем инвертирования выхода логического элемента И-НЕ, как показано ниже.

| Желаемое И Ворота | Строительство NAND | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = А И B | = ( А NAND B ) NAND ( А NAND B ) | |||||||||||||||

| ||||||||||||||||

ИЛИ ЖЕ

Если проверяется таблица истинности для логического элемента И-НЕ или применяя Законы Де Моргана, можно увидеть, что если любой из входов равен 0, то выход будет равен 1. Однако, чтобы быть логическим элементом ИЛИ, выход должен быть 1, если какой-либо вход равен 1. Следовательно, если входы инвертированы, любой высокий input вызовет высокий выходной сигнал.

| Желаемый OR Gate | Строительство NAND | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = А ИЛИ ЖЕ B | = ( А NAND А ) NAND ( B NAND B ) | |||||||||||||||

| ||||||||||||||||

НИ

Вентиль ИЛИ-ИЛИ - это вентиль ИЛИ с инвертированным выходом. Выход высокий, когда ни на входе A, ни на входе B нет высокого уровня.

| Желаемые ворота NOR | Строительство NAND | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = А НИ B | = [ ( А NAND А ) NAND ( B NAND B )] NAND [ ( А NAND А ) NAND ( B NAND B ) ] | |||||||||||||||

| ||||||||||||||||

XOR

Вентиль XOR создается путем соединения четырех ворот NAND, как показано ниже. Эта конструкция влечет за собой задержку распространения в три раза по сравнению с одиночным вентилем И-НЕ.

| Желаемый шлюз XOR | Строительство NAND | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = А XOR B | = [ А NAND ( А NAND B )] NAND [ B NAND ( А NAND B ) ] | |||||||||||||||

| ||||||||||||||||

В качестве альтернативы, вентиль XOR создается с учетом дизъюнктивная нормальная форма , отмечая от закон де Моргана что вентиль И-НЕ является вентилем ИЛИ с инвертированным входом. В этой конструкции используется пять ворот вместо четырех.

| Желаемые ворота | Строительство NAND |

|---|---|

|  |

| Q = А XOR B | = [ B NAND ( А NAND А )] NAND [ А NAND ( B NAND B ) ] |

XNOR

Строб XNOR создается с учетом дизъюнктивная нормальная форма , отмечая от закон де Моргана что вентиль И-НЕ является вентилем ИЛИ с инвертированным входом. Эта конструкция влечет за собой задержку распространения в три раза по сравнению с одиночным вентилем И-НЕ и использует пять вентилей.

| Желаемый XNOR Gate | Строительство NAND | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = А XNOR B | = [ ( А NAND А ) NAND ( B NAND B )] NAND ( А NAND B ) | |||||||||||||||

| ||||||||||||||||

В качестве альтернативы, 4-вентильная версия логического элемента XOR может использоваться с инвертором. Эта конструкция имеет задержку распространения в четыре раза (вместо трех), чем у одного логического элемента И-НЕ.

| Желаемые ворота | Строительство NAND |

|---|---|

|  |

| Q = А XNOR B | = { [ А NAND ( А NAND B )] NAND [ B NAND ( А NAND B )]} И-НЕ { [ А NAND ( А NAND B ) ] NAND [ B NAND ( А NAND B ) ] } |

MUX

А мультиплексор или вентиль MUX - вентиль с тремя входами, который использует один из входов, называемый бит селектора, для выбора одного из двух других входов, называемых биты данных, и выводит только выбранный бит данных.[1]

| Желаемый шлюз MUX | Строительство NAND | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Q = [ А И НЕТ( S ) ] ИЛИ ЖЕ ( B И S ) | = [ А NAND ( S NAND S ) ] NAND ( B NAND S ) | ||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||

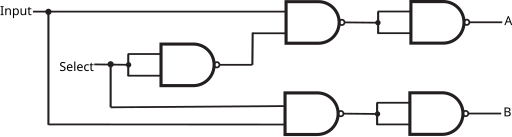

DEMUX

Демультиплексор выполняет функцию, противоположную мультиплексору: он принимает один вход и направляет его на один из двух возможных выходов в соответствии с битом селектора, который указывает, какой выход выбрать.[1]

| Желаемый DEMUX Gate | Строительство NAND | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||

| |||||||||||||||||||||

Смотрите также

- Инсульт Шеффера - другое имя

- НИ логика. Как и ворота NAND, ворота NOR также являются универсальными воротами.

- Функциональная полнота

внешняя ссылка

Рекомендации

- ^ а б Нисан, Н. & Шокен, С., 2005. В: От NAND к тетрису: построение современного компьютера от первых принципов. s.l.: MIT Press, стр. 20. Доступно по адресу: http://www.nand2tetris.org/chapters/chapter%2001.pdf В архиве 2017-01-10 в Wayback Machine

- Ланкастер, Дон (1974). Поваренная книга TTL (1-е изд.). Индианаполис, Индиана: Ховард В. Сэмс. стр.126–135. ISBN 0-672-21035-5.

- Шеффер, Х. М. (1913), "Набор из пяти независимых постулатов для булевых алгебр с применением к логическим константам", Труды Американского математического общества, 14: 481–488, Дои:10.2307/1988701, JSTOR 1988701